Product Summary

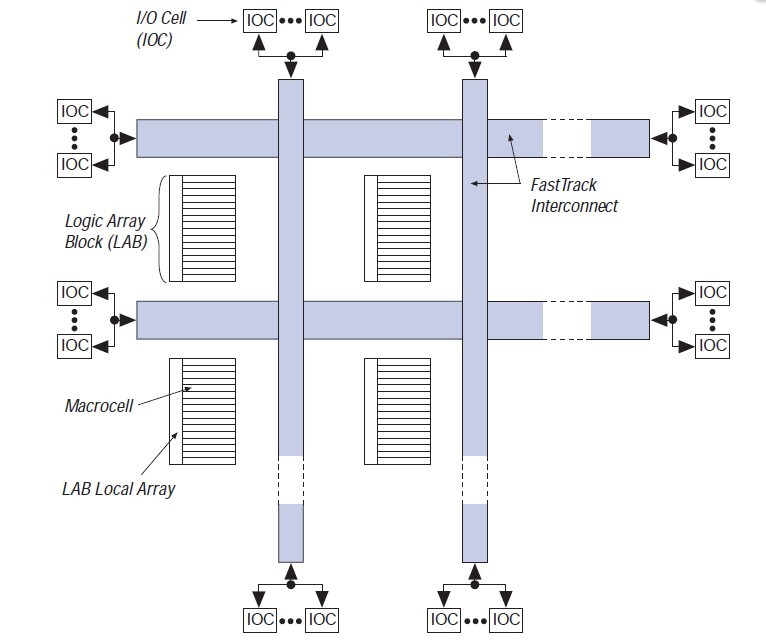

The EPM9320RC208-15N is a in-system-programmable, high-density, highperformance EPLD which is based on the third-generation MAX architecture of Altera. Fabricated on an advanced CMOS technology, the EPM9320RC208-15N provides 6,000 to 12,000 usable gates, pin-to-pin delays as fast as 10 ns, and counter speeds of up to 144 MHz.

UDN1330A

UDN2069B

UDN2544A

UDN2588N

UDN2588R

UDN2590Z

UDN2597A

UDN2935Z

UDN2950I

UDN2950Z

UDN2953BIC

UDN2954W

UDN2956B

UDN2956R

UDN2980A

UDN2982A

UDN2984ABU

UDN5707B

UDN5712M

UDN6118A

UDORSP

UDQ2588A

UDS6118R

UDX2952B

UDZ/5.6B

UDZ10B/05/10V

UDZ11B-7

UDZ6.2B/

UDZ8.2B/

UDZS 15B

UDZS 16B

UDZS22VB

UDZS3.0B--

UDZS3.6B

UDZS5.1V

UDZSTE17-16B

UDZS-TE-17-5.1B

UDZTE-1710B

UDZV5.1B

UDZV6.2B

UE204011

104-T

UFMMT717

UFR10130

UFS120-T

UF-S1-YM

UFT15015

UFT21020

UFT40130

UFT40280

UG1001-T

UG1004-A

UG10053A

UG1005-LIT

UG1007TB

UG10224C

UG10601A

UG12R85A

UG16CCT

UG-210/U

UG2392-B

UG306B/U

UG3101(C)USE

UG-314/U

UG-499/U

UG4D5703

UG-6028G

UG80486DX4WB100

UG-89C/U

UG-909/U

UG-977/U

UGB18DCT

UGB8JT/31

UGF2005P

UGF8J C0

UGN3019U

UGN3020T

UGN3120U

UGN3131U

UGTZ4-414A

UGWP2USHN33

UH40155

UH8615

UHA1H100KHA

UHBS30-1

UHBS30-2

UHBS60-2

UHD403-1MIL

UHE0J272

UHF-C-18

UHIC003

UHJ144840002

UHJ422690007

UHP408-1

UIC811-D

UIC811G-B

UICPP2L4BL

UINK2FWH

UINK4FWH

UIWOL3-L

UJ206020

UJ260953

UJ3507BN

UJ360016

UJ360501

UJ361168

UJ760013

UK003002

UK-018RG

UK10N BU

UK120874

UK-1260G

UK220705C

UK250103

UK25563M

UK-5N

UK70A-ES

UKA1A102MPD1TD

UKK 5-PV

UKN09G-910

UKN09H-240

UKN27J-015

For more information or to order consultation, please EMAL us directly.

Parametrics

EPM9320RC208-15N absolute maximum ratings: (1)On the condition of with respect to ground, VCC Supply voltage: min=-2.0V, max=7.0V; (2)On the condition of with respect to ground, VI DC input voltage min=-2.0V, max=7.0V; (3)On the condition of with respect to ground, VCCISP Supply voltage during in-system programming: min=-2.0V, max=7.0V; (4)IOUT DC output current, per pin: min=-25mA, max=25mA; (5)On the condition of No bias, TSTG Storage temperature: min=-65℃, max=150℃; (6)On the condition of Under bias, TAMB Ambient temperature: min=-65℃, max=135℃; (7)On the conditions of Ceramic packages, under bias, TJ Junction temperature: max=150℃; On the conditions of PQFP and RQFP packages, under bias: max=135℃.

Features

EPM9320RC208-15N features: (1)High-performance CMOS EEPROM-based programmable logic devices (PLDs) built on third-generation Multiple Array MatriX (MAX) architecture; (2)5.0-V in-system programmability (ISP) through built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface; (3)Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990; (4)High-density erasable programmable logic device (EPLD) family ranging from 6,000 to 12,000 usable gates (see Table 1); (5)10-ns pin-to-pin logic delays with counter frequencies of up to 144 MHz.

Diagrams

|

EPM900 |

Keil Tools |

Emulators / Simulators EMULATOR PROGRAMMER FOR PHILIPS P89LPC9x |

Data Sheet |

Negotiable |

|

||||||||

|

EPM9320LC84-15 |

|

IC MAX 9000 CPLD 320 84-PLCC |

Data Sheet |

|

|

||||||||

|

EPM94CKW-1060 |

Honeywell |

Toggle Switches SEALED OI |

Data Sheet |

|

|

||||||||

|

EPM94CKW-1061 |

Honeywell |

Toggle Switches SEALED OI |

Data Sheet |

|

|

||||||||

|

EPM94CKW-1062 |

Honeywell |

Toggle Switches SEALED OI |

Data Sheet |

|

|

||||||||

|

EPM94CKW-1064 |

Honeywell |

Toggle Switches SEALED OI |

Data Sheet |

|

|

||||||||

(China (Mainland))

(China (Mainland))